# THE LEBANESE AMERICAN UNIVERSITY GRADUATE STUDIES

| We hereby approve the thesis of                                  |

|------------------------------------------------------------------|

| Salam Harfoush                                                   |

| candidate for the Master of Science degree in Computer Science.* |

| Signed: - (Chairman)                                             |

|                                                                  |

|                                                                  |

| <u> </u>                                                         |

Date April 3, 47

<sup>\*</sup>We also certify that written approval has been obtained for any proprietary material contained therein.

I grant to the Lebanese American University the right to use this work, irrespective of any copyright, for the University's own purposes without cost to the University or to its students, agents and employees. I further agree that the University may reproduce and provide single copies of the work, in any format other than in or from microforms, to the public for the cost of reproduction.

RT 346

# AN APPROACH TO REDESIGN FOR TESTABILITY AT THE RT LEVEL USING BIST TECHNIQUES

by

#### SALAM S. HARFOUCHE

Submitted in partial fulfillment of the requirements for the Degree of Master of Science

Thesis Advisor: Dr. Haidar M. Harmanani

Department of Computer Science Lebanese American University—Byblos June 1997

# An Approach to Redesign for Testability at the RT Level Using BIST Techniques

#### **ABSTRACT**

by

#### SALAM S. HARFOUCHE

The increasing density in VLSI chips complicates the design as well as it complicates the testability problem. This thesis proposes a new approach to redesign for testability at the Register Transfer Level (RTL). Given an RTL description of a data path, the purpose of the redesign process is to improve its testability with a minimal cost by: 1) inserting additional registers, if necessary; 2) Converting already existing registers into test registers so that they can be configured as TPGRs, MISRs, or BILBOs during test mode. In order to reduce test penalty, and insure the data path structural testability, it is necessary to automate the BIST Insertion process. BIST registers are chosen so that to minimize test and time overhead, by using Randomness and Transparency metrics of the combinational logic.

To my parents

#### **ACKNOWLEGMENTS**

I would like to thank my thesis advisor Dr. Haidar Harmanani for his guidance. Also, I would like to thank Dr. W. Keirouz and Dr. G. E. Nasr for being on my thesis committee.

I would like to thank my friends at the Lebanese American University for all their support during my studies.

Finally, I would like to thank my family for their support, and to extand my gratitude to the Hariri Foundation and to the Lebanese American University who helped me financially to accomplish this work.

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION       1         1.1 THE ABSTRACTION LEVELS       1         1.2 TESTING       2         1.3 HIGH LEVEL SYNTHESIS       3         1.3 HIGH LEVEL SYNTHESIS       3         1.3.1 High Level Synthesis Steps       6         1.4 DESIGN FOR TESTABILITY       7         1.4.1 Scan Technique       8         1.5 PROBLEM DEFINITION AND THESIS OUTLINE       9         CHAPTER 2: LITERATURE REVIEW       11         2.1 ADEPT       11         2.2 SYNTEST       12         2.3 BREUER'S BILBO METHODOLOGY       13         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       15         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       21         3.2 TEST POINT MINIMIZATION       27         3.3 THE SCHEDULING PROCESS       34         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 3       43         4.5 EXAMPLE 5       45         4.6 CONCLUSION       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----|

| 1.1 THE ABSTRACTION LEVELS       2         1.2 TESTING       3         1.3 HIGH LEVEL SYNTHESIS       3         1.3.1 High Level Synthesis Steps       6         1.4 DESIGN FOR TESTABILITY       7         1.4.1 Scan Technique       8         1.4.2 BIST Technique       9         1.5 PROBLEM DEFINITION AND THESIS OUTLINE       9         CHAPTER 2: LITERATURE REVIEW       11         2.1 ADEPT       12         2.2 SYNTEST       13         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       15         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3: REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       24         3.2 TEST POINT MINIMIZATION       27         3.4 THE SCHEDULING PROCESS       34         CHAPTER 4: RESULTS       36         4.1 EXAMPLE 1       38         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHAPTER 1: INTRODUCTION                      | 1  |

| 1.2 TESTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              | 1  |

| 1.3 High Level Synthesis Steps.       3         1.4 Design For Testability.       7         1.4.1 Scan Technique.       8         1.4.2 BIST Technique.       9         1.5 Problem Definition and Thesis Outline.       9         CHAPTER 2: LITERATURE REVIEW.       11         2.1 ADEPT.       12         2.2 SYNTEST.       13         2.3 Breuer's BILBO Methodology       13         2.4 A Behavioral Level Synthesis for Testability System       15         2.5 Automatic Insertion of BIST Hardware (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 The different testing considerations       21         3.2 Test point minimization       24         3.3 The selection process       34         CHAPTER 4: RESULTS       36         4.1 Example 1       39         4.2 Example 2       41         4.3 Example 3       43         4.4 Example 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.1 Treting                                  | 2  |

| 1.3.1 High Level Synthesis Steps.       6         1.4 Design For Testability       7         1.4.1 Scan Technique       8         1.5 Problem Definition and Thesis Outline       9         CHAPTER 2: LITERATURE REVIEW       11         2.1 ADEPT       12         2.2 SYNTEST       13         2.3 Breuer's BILBO Methodology       15         2.4 A Behavioral Level Synthesis for Testability System       15         2.5 Automatic Insertion of BIST Hardware (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 The different testing considerations       21         3.2 Test point minimization       24         3.3 The selection process       34         3.4 The Scheduling Process       34         CHAPTER 4: RESULTS       36         4.1 Example 1       39         4.2 Example 2       41         4.3 Example 3       43         4.4 Example 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |    |

| 1.4 DESIGN FOR TESTABILITY  1.4.1 Scan Technique  1.5 PROBLEM DEFINITION AND THESIS OUTLINE  CHAPTER 2: LITERATURE REVIEW  11  2.1 ADEPT  2.2 SYNTEST  2.3 BREUER'S BILBO METHODOLOGY  2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM  2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)  1.6  CHAPTER 3: REDESIGN FOR TESTABILITY  3.1 THE DIFFERENT TESTING CONSIDERATIONS  3.2 TEST POINT MINIMIZATION  3.3 THE SELECTION PROCESS  3.4 THE SCHEDULING PROCESS  3.4 THE SCHEDULING PROCESS  3.5 CHAPTER 4: RESULTS  4.1 EXAMPLE 1  3.2 EXAMPLE 2  4.3 EXAMPLE 3  4.4 EXAMPLE 4  4.5 EXAMPLE 4  4.5 EXAMPLE 4  4.5 EXAMPLE 4  4.6 EXAMPLE 4  4.7 EXAMPLE 4  4.7 EXAMPLE 4  4.8 EXAMPLE 4  4.9 EXAMPLE 4  4.9 EXAMPLE 4  4.1 EXAMPLE 4  4.1 EXAMPLE 4  4.3 EXAMPLE 4  4.4 EXAMPLE 4  4.5 EXAMPLE 4  4.6 EXAMPLE 4  4.7 EXA | 1.3 High Level Synthesis Steps               | 6  |

| 1.4.1 Scan Technique       8         1.4.2 BIST Technique       9         1.5 PROBLEM DEFINITION AND THESIS OUTLINE       9         CHAPTER 2: LITERATURE REVIEW         11       2.1 ADEPT       11         2.2 SYNTEST       12         2.3 BREUER'S BILBO METHODOLOGY       13         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       15         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       24         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       34         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.4. Departure For Test Arill ITY            | 7  |

| 1.4.2 BIST Technique       9         1.5 PROBLEM DEFINITION AND THESIS OUTLINE       11         CHAPTER 2: LITERATURE REVIEW       11         2.1 ADEPT       12         2.2 SYNTEST       12         2.3 BREUER'S BILBO METHODOLOGY       13         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       15         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       21         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         CHAPTER 4: RESULTS       36         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.4 1 Com Tochnique                          | 8  |

| 1.5 PROBLEM DEFINITION AND THESIS OUTLINE  CHAPTER 2: LITERATURE REVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.4.2 DIST Technique                         |    |

| CHAPTER 2: LITERATURE REVIEW       11         2.1 ADEPT       12         2.2 SYNTEST       13         2.3 BREUER'S BILBO METHODOLOGY       15         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       15         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       21         3.2 TEST POINT MINIMIZATION       24         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       34         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.5 PROPERTY DEFINITION AND THESIS OUTLINE   |    |

| 2.1 ADEPT       12         2.2 SYNTEST       13         2.3 BREUER'S BILBO METHODOLOGY       13         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       15         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       21         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       34         CHAPTER 4: RESULTS       36         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.3 FROBLEM DETRITIONAL                      | 11 |

| 2.1 ADEPT       12         2.2 SYNTEST       13         2.3 BREUER'S BILBO METHODOLOGY       13         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       15         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       21         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       34         CHAPTER 4: RESULTS       36         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHAPTER 2: LITERATURE REVIEW                 | 11 |

| 2.2 SYNTEST       13         2.3 BREUER'S BILBO METHODOLOGY       15         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       16         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       16         CHAPTER 3: REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       21         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       36         CHAPTER 4: RESULTS       36         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              | L  |

| 2.3 BREUER'S BILBO METHODOLOGY       15         2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY SYSTEM       16         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       19         CHAPTER 3:REDESIGN FOR TESTABILITY       19         3.1 THE DIFFERENT TESTING CONSIDERATIONS       21         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       34         CHAPTER 4: RESULTS       36         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.2 CVNTEST                                  | 12 |

| 2.4 A BEHAVIORAL LEVEL SYNTHESIS FOR TESTABILITY       16         2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIBH)       19         CHAPTER 3:REDESIGN FOR TESTABILITY       21         3.1 THE DIFFERENT TESTING CONSIDERATIONS       24         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       36         CHAPTER 4: RESULTS       38         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |    |

| 2.5 AUTOMATIC INSERTION OF BIST HARDWARE (AIDH)       19         CHAPTER 3:REDESIGN FOR TESTABILITY       21         3.1 THE DIFFERENT TESTING CONSIDERATIONS       24         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       36         CHAPTER 4: RESULTS       38         4.1 EXAMPLE 1       39         4.2 EXAMPLE 2       41         4.3 EXAMPLE 3       43         4.4 EXAMPLE 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |    |

| CHAPTER 3:REDESIGN FOR TESTABILITY         3.1 THE DIFFERENT TESTING CONSIDERATIONS       24         3.2 TEST POINT MINIMIZATION       27         3.3 THE SELECTION PROCESS       34         3.4 THE SCHEDULING PROCESS       36         CHAPTER 4: RESULTS       36         4.1 Example 1       39         4.2 Example 2       41         4.3 Example 3       43         4.4 Example 4       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | O. S. ANTION CATION OF BIST HARDWARE (ALDIT) |    |

| 3.1 THE DIFFERENT TESTING CONSIDERATIONS 24 3.2 TEST POINT MINIMIZATION 27 3.3 THE SELECTION PROCESS 34 3.4 THE SCHEDULING PROCESS 34  CHAPTER 4: RESULTS 36 4.1 EXAMPLE 1 39 4.2 EXAMPLE 2 41 4.3 EXAMPLE 3 43 4.4 EXAMPLE 4 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Z.5 AUTOMATIO INDICATA DI ITV                | 19 |

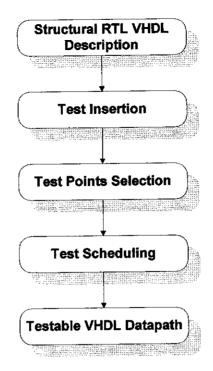

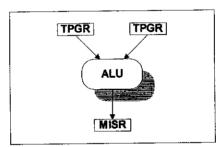

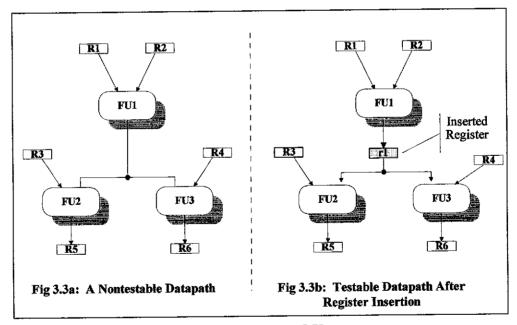

| 3.2 TEST POINT MINIMIZATION 27 3.3 THE SELECTION PROCESS 34 3.4 THE SCHEDULING PROCESS 36  CHAPTER 4: RESULTS 38 4.1 Example 1 39 4.2 Example 2 41 4.3 Example 3 43 4.4 Example 4 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CHAPTER 3:REDESIGN FOR TESTABILITY           | 21 |

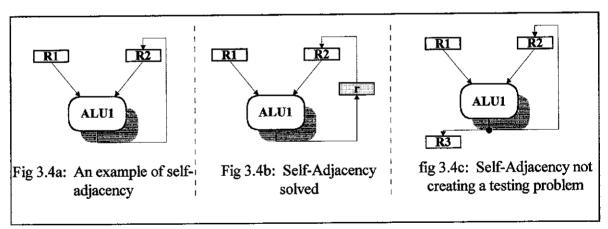

| 3.2 TEST POINT MINIMIZATION 27 3.3 THE SELECTION PROCESS 34 3.4 THE SCHEDULING PROCESS 36  CHAPTER 4: RESULTS 38 4.1 Example 1 39 4.2 Example 2 41 4.3 Example 3 43 4.4 Example 4 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 1 THE DIFFERENT TESTING CONSIDERATIONS     | 24 |

| 3.3 THE SELECTION PROCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.2 Treet point minimization                 | 27 |

| 3.4 THE SCHEDULING PROCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 3 Tue sei ection process                   | 34 |

| CHAPTER 4: RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.4 Tree Schedul ING PROCESS                 |    |

| 4.1 Example 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | J.7 1116 Solitabolate                        | 36 |

| 4.2 EXAMPLE 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CHAPTER 4: RESULTS                           | 38 |

| 4.2 EXAMPLE 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A 1 FYAMPLE 1                                | 30 |

| 4.3 EXAMPLE 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.1 EXAMPLE 2                                | 41 |

| 4.4 Example 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2 EVAMPLE 3                                | 43 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AA EVAMPLE4                                  | 45 |

| 4.6 CONCLISION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.6 CONCLUSION                               |    |

## LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

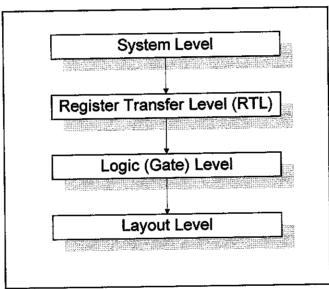

| FIGURE 1.1: THE ABSTRACTION LEVELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  |

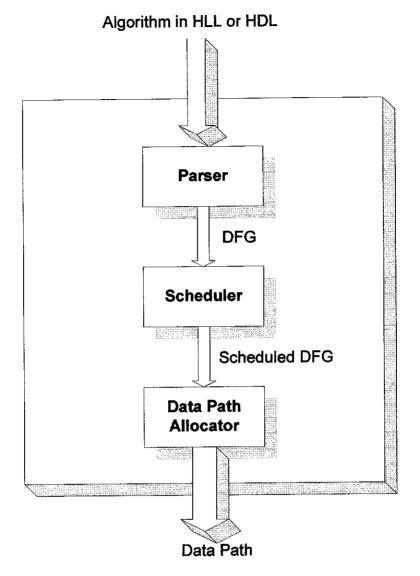

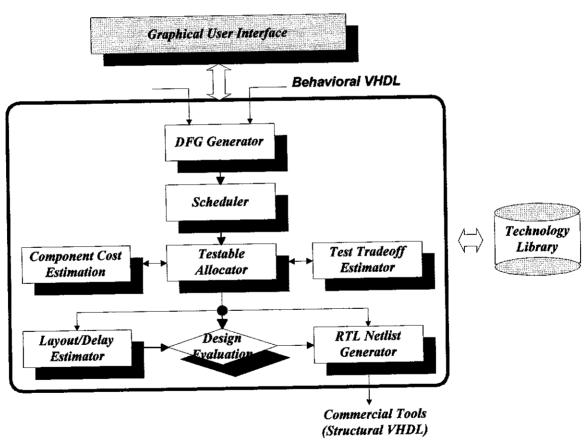

| A TO COMPANY OF TRACT A PARTY SANTUESIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

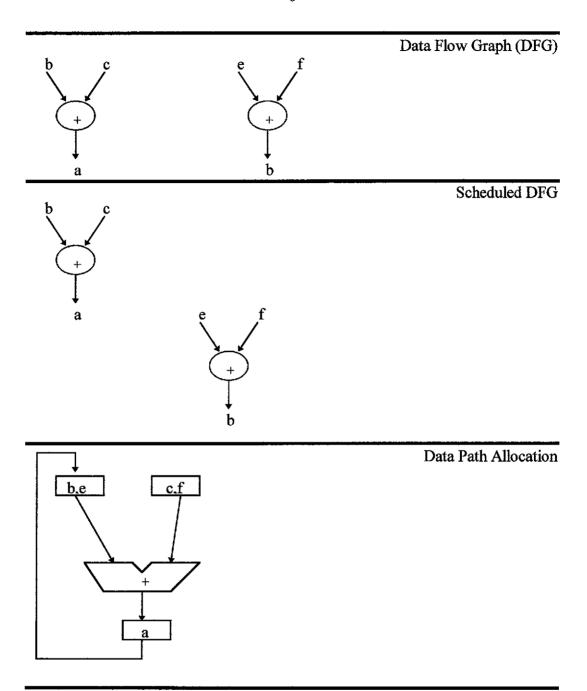

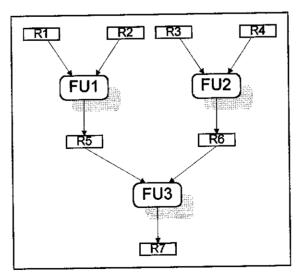

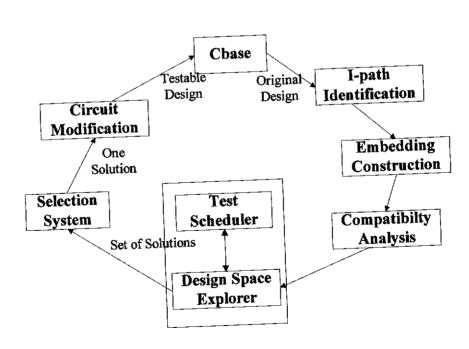

| TI THE TAX OF CAMPUTATION AND A SECOND SECON |    |

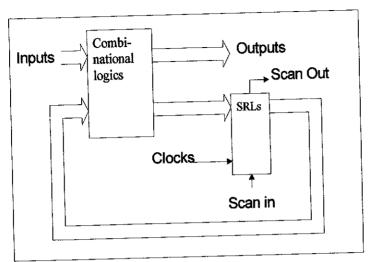

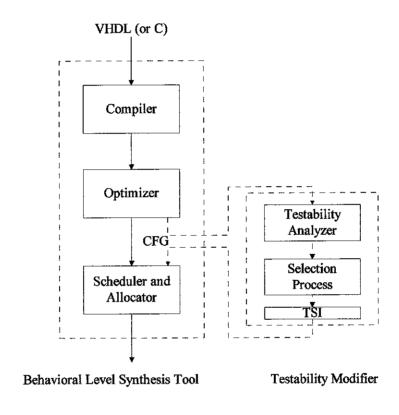

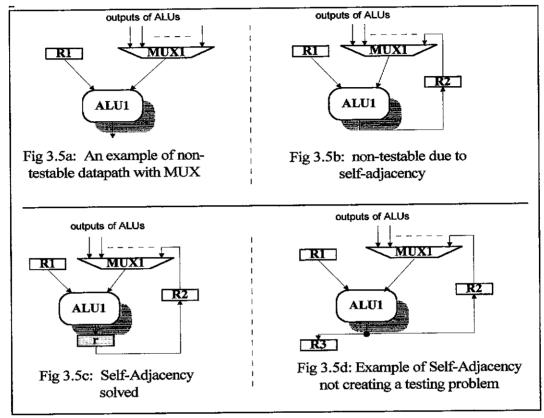

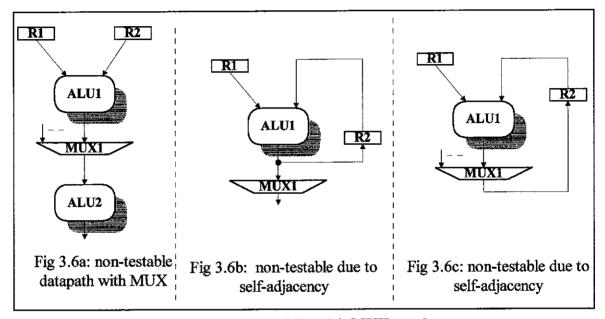

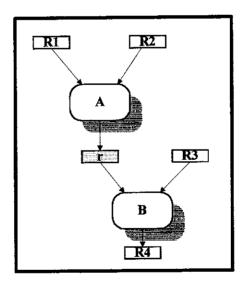

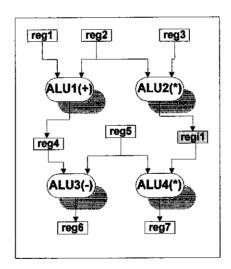

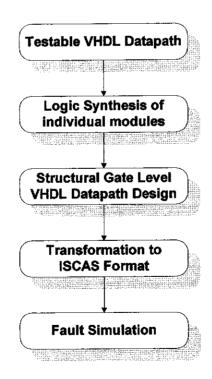

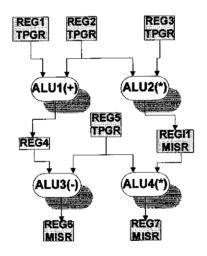

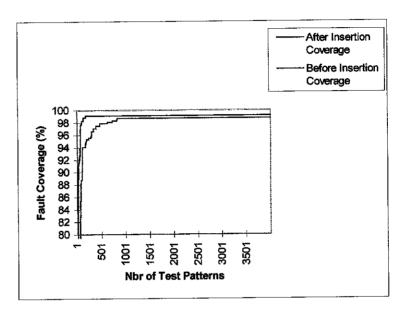

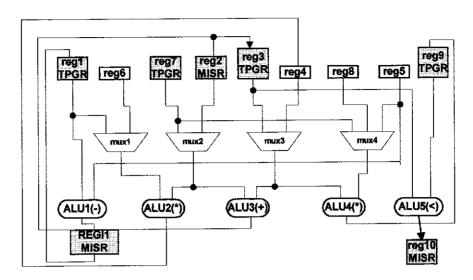

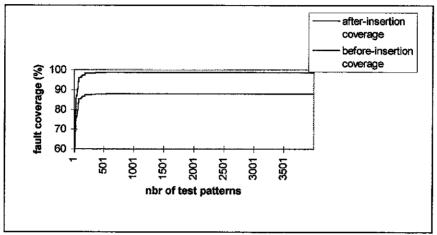

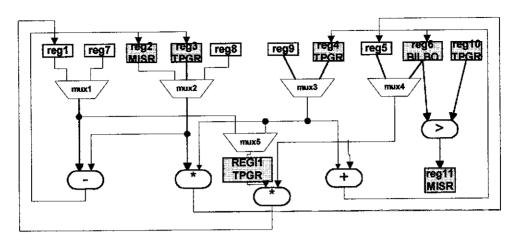

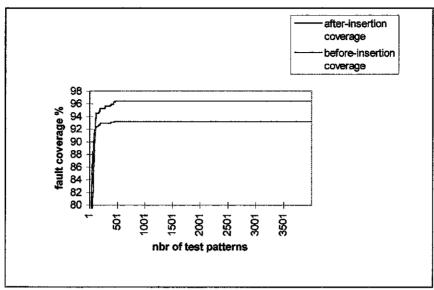

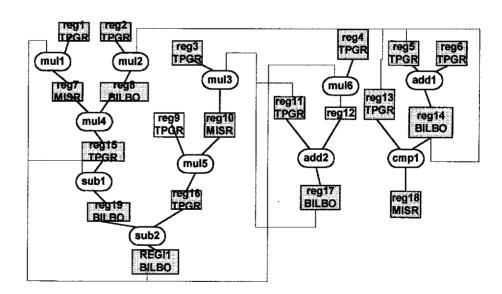

| D. core Drotosi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |